1.系统安全芯片硬件设计

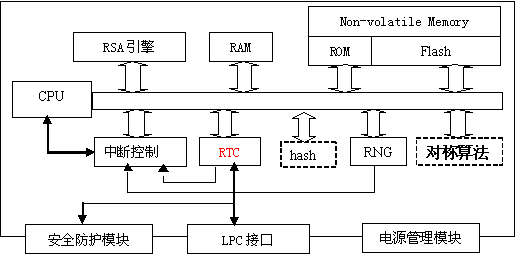

TPM芯片是一款SOC(System-on-Chip)芯片,内部集成了CPU核、RAM、ROM、Flash、加密算法协处理器、随机数生成器等模块,COS系统和配套的应用软件,主要用于完成计算机平台可靠性认证、用户身份认证、数字签名等功能。其硬件结构描述如图4所示。

图 4 TPM芯片硬件总体结构图

散列算法模块(HASH):硬件实现散列算法:SHA-1及散列消息鉴别码HMAC。

非对称密码协处理器模块(RSA):协处理器作为硬件算法加速器,主要完成模幂,模乘,模加运算。协处理器以改进的蒙格马利算法为基础,以位加法器和位乘法器为核心,通过使用总线仲裁、总线冻结及流水线等设计手段和设计技术完成算法的硬件加速功能。

真随机数产生模块(RNG):真随机数产生器,快速生成各种安全运算所需的随机数。

安全防护模块:采用电流平衡分布设计技术防止能量攻击,采用硬件访问控制技术和存储加密技术来保护片上敏感信息。

LPC接口模块:LPC总线接口模块,符合Low pin count总线协议,是TPM芯片与外部交换数据的窗口。

中断控制模块:中断控制器IP软核。

CPU:32位RISC CPU硬核。

RAM:主要用作核心软件模块的运行和高速结果暂存。

Flash:用于COS系统静态存储,升级及保存密钥 、证书及标志。

时钟管理模块:按照ACPI协议的电源管理要求,实现动态时钟管理,当总线和总线上的模块在不选中的时候,以及安全芯片在一段时间内没有使用之后,将时钟频率降低,以降低功耗。

(责任编辑:adminadmin2008)